인텍플러스를 검색하다가, 미래에셋증권의 반도체 산업 보고서를 보게 되었다.

내용이 상당히 방대해서 찬찬히 읽어볼 생각이긴한데, 결론과 요약을 잘 정리를 해두셔서 그 내용만 우선 블로그에 올려놓아 본다.

자료 전체의 결론 및 Implication

1부에서는 반도체 소자의 발전 방향과 그에 따른 투자 기회를 찾고자 한다.

Logic 반도체에서는 50년의 반도체 역사상 두번째로 진행되는 MOSFET의 구조 변화가 임박했다.

GAA 구조 채용에 따라 Si/SiGe 박막 Epitaxy 장비의 수요가 늘어날 것으로 전망한다. 소재의 측 면에서는 Si/SiGe 박막 Epitaxy에 사용되는 Si과 Ge 프리커서의 수요 또한 증가할 것으로 예상된 다. 또한, 박막 증착 이후, SiGe를 선택적으로 제거하는 공정이 추가된다. 관련 Etchant의 수요 확 대가 전망된다. 파운드리 업체들의 본격적인 EUV 기반 생산경쟁까지는 불과 1년여 밖에 남지 않았다. 그 사이 삼 성전자는 EUV의 수율과 가동률을 높일 수 있는 생태계를 구축해야만 하는 상황이다. EUV 도입의 의미는 장비 확보 그 자체에 그치지 않는다. Stepper 뿐만 아니라 Photoresist, Photomask, Pellicle, Inspection 등 기존 시스템과 다른 전반적인 생태계를 조성해야 하는 분야다. 관련 서플 라이체인의 수혜가 예상된다.

DRAM에서는 3D 구조와 Capacitor 소재의 변화에서 중장기적인 수혜 영역을 찾을 수 있다.

DRAM의 현재 구조는 트랜지스터 상부에 수직으로 Capacitor를 쌓은 구조로 발달해왔다. 더 이상 의 수평 구조상 변경은 설계 및 공정의 한계로 불가능하다. 현재의 구조를 유지한 채 종횡비만을 올리기에는 한계에 달하면서 향후 DRAM의 구조의 3D DRAM으로의 논의가 시작되고 있다. 3D DRAM의 경우 적층의 방식이 Si/SiGe Epitaxy 등을 이용한 단결정 적층 방식이 될 가능성이 높다. Si/SiGe Selective Etching은 HF/H2O2/CH3COOH를 이용한 Wet Etching 방식이 유력 하다. 3D DRAM의 횡방향 Capacitor 표면의 유전체 증착을 위한 ALD 수요 또한 증가할 것이다. 향후 5년간은 현재 DRAM의 Capacitor의 구조를 유지한 채 정전용량(Capacitance)를 극한으로 높일 가능성이 높다. 현재의 DRAM Capacitor는 ZAZ 유전막에 TiN 전극을 사용하고 있는데, 이 후 유전막은 TiO2 등으로 변경되며 동시에 전극도 Ru(Ruthenium)으로 변경하기 위한 연구개발 이 지속되고 있다. 관련 Precursor에 주목해야 한다. NAND에서는 Double Stacking의 보편화, Pitch 사이즈 축소, Bonding 중요성 증대가 전망된다. 삼성전자를 마지막으로 Double Stacking이 업계 전반에 보편화 되었다. Double stacking은 기존 의 Single stacking 대비 HARC etching의 횟수가 2배로 늘어나고, Etching을 위한 Hardmask를 한번씩 더 사용해야 한다. 또한, Focus ring의 Plasma 노출 횟수도 Stacking 횟수에 비례해 증가 하게 될 것이다. 또한, Oxide-Nitride 단수 증가에 따른 장비/소재의 자연 증가도 기대된다. 공정에 사용되는 박막 소재들의 수요도 비례해 증가할 전망이다. 현재 100단대의 NAND가 24년부터는 300단대에 진입 할 것으로 전망된다. 단수가 증가하는 가운데 칩 두께를 유지하기 위해서는 Vertical pitch는 24년 30nm대로 진입할 것으로 전망된다. NAND가 200단 후반으로 진입하게 되면서 Cell당 Vertical pitch가 30nm대에 진입할 것으로 전망된다. 24년부터는 기존의 Word Line 배선 W(텅스텐)의 저 항이 급격하게 올라가기 때문에 저항이 낮은 물질로 변경될 가능성이 높다.

2부에서는 반도체 단위 공정의 기본적인 작동 메커니즘과 구성 서플라이체인, 향후 기술의 발전 방향에 따른 수혜영역을 다루었다. 발전 방향과 수혜 영역을 위주로 요약하자면,

Wafer 업종:

NAND와 후공정 분야에서의 Wafer Bonding 공정 적용 증가로 인해 Wafer 수량의 자연 증가가 전망된다. 또한, SiC Wafer 수요 확대 가운데 관련 체인의 기업가치 상향이 기대된다.

노광공정:

23년 출시예정인 EUV부터는 본격적인 Through put 향상이 계획되어 있다. Wafer 처 리량이 증가함에 따라 노광 횟수에 비례해 증가하는 포토마스크, 펠리클 등 관련 부품의 사용량 증 가가 예상되며, 특히 포토마스크 노출 횟수의 증가는 Inspection 수요 증가를 유발할 것으로 기대 한다. 또한, EUV용 차세대 PR 개발 경쟁 가운데 신규 진입자의 진입 기회가 될 것으로 판단한다.

식각공정:

3D NAND 고단화에 따른 유전체 식각 공정에서의 플라즈마 노출 강도 및 빈도의 증가 로 SiC Ring 소모량 증가에 따른 수요 증가가 기대된다. 또한, Logic 소자의 FinFET → GAA 변경 으로 인한 트랜지스터 공정 Step 증가로 전도체 Dry Etcher 수요도 증가할 것으로 전망한다. GAA 소자 공정시에 SiGe Selective Etching 레시피인 Etchant 사용량 증가도 예상된다.

열공정:

소자의 미세화에 따른 RTA 노출 타이밍 최소화 요건이 심화되며 Laser Annealing 장비 채용 기조가 확대될 전망이다. 기존 Furnace 장비의 경우 TEL 과점 상태(Diffusion 및 LP-CVD) 로 인해 TEL 향 Diffusion Quartz Tube 수요가 견조 견조할 것으로 예상한다.

증착공정:

메모리 소자 고도화에 따른 ILD, IMD 저온 증착 수요 증대로 저온 증착이 가능한 PE-CVD와 저온 유전체용 Si 프리커서의 수요 확대가 기대된다. ALD의 수요는 소자와 공정의 구조적 방향성에 따라 증가할 것이다. 특히, 근본적 약점인 Through put 개선에 대한 관심도가 높으며 공 간분할을 통해 ALD 리드타임을 최소화 시키는 SD-ALD장비의 수요가 강할 것으로 전망한다.

메탈공정:

시장의 크기가 작음에도 불구하고 도금 공정이 반도체 8대 공정중 필수 공정일 뿐만 아 니라 Foundry 공정에서는 중요도가 더욱 높아지는 공정인 점을 고려할 때, ECD 장비에 대한 독점 적 지위를 누리고 있는 업체의 높은 수익성과 전사 밸류에이션을 뒷받침 할 수 있는 요인으로 판 단한다. 독점 장비의 경우 가격 협상력 차원에서 우위를 점할 수 있기 때문이다.

CMP공정:

Logic 소자의 경우, GAA로의 트랜지스터 구조 변경에 따라서도 Gate에 대한 III-V족 소재 적용, Co Interconnect 적용 등에 따른 신규 CMP Layer 증가 효과가 기대된다. 메모리에서 는 DRAM Peri 영역에서의 FinFET 적용은 CMP 적용 Layer가 5개 이상 늘어나는 효과를 유발할 수 있을 것이다. NAND의 경우 더블스테킹 공정이 대중화 됨에 따라 텅스텐 워드라인과 ILD층 위 주로 CMP 수요 증가가 예상된다.

세정공정:

CMP 공정의 경우 파티클과 금속물질의 잔류량이 많아 Post CMP Cleaning으로 분류할 만큼 세정의 중요성이 높다. 앞서 다뤘듯이 CMP 공정의 Step 수가 늘어날수록 세정공정의 수요 또한 증가할 것으로 전망한다. 또한, 최근 환경문제에 관심도가 높아지며 Dry Cleaning의 개발이 이뤄지고 있다. 신규 시장의 성격으로 작용할 가능성이 높다고 판단한다.

Test & Packaging 공정:

글로벌 파운드리 Big 3사의 차세대 Packaging 로드맵 확장이 적극적임 에 따라 이에 동반한 기판 및 부품 소재의 증가가 기대된다. 또한, Packaging 공정에서 Bonding 의 중요도가 높아지는 추세임에 주목할 필요가 있다. Packaging이 다양해지고 고도화 될 수록 Test 또한 고도화 될 것으로 전망하며 이는 Test House의 중요도가 증대되고 Test 관련 소모품 의 사용량 증가로 이어질 것으로 전망한다.

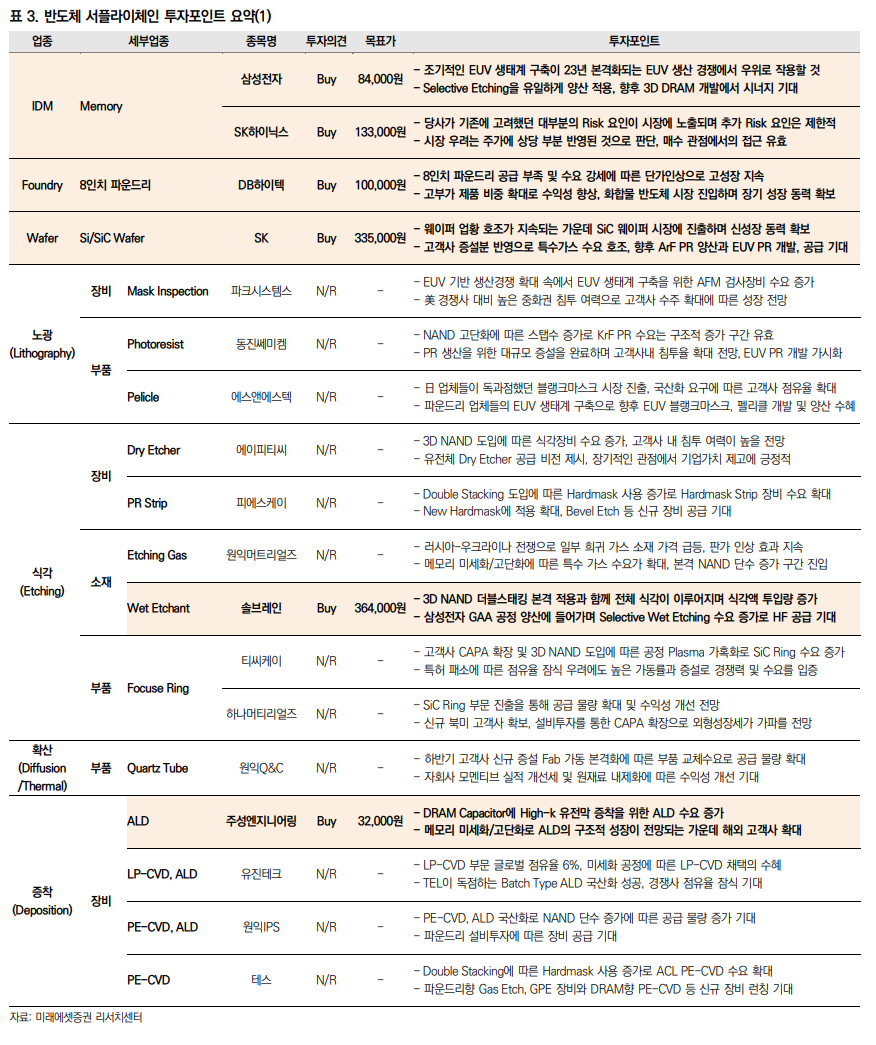

상기 소자와 공정의 변화 요인으로부터 투자포인트를 삼아, 관심 종목으로는 삼성전자(005930), SK하이닉스(000660), 주성엔지니어링(036930), 피에스케이(319660), 유진테크(084370), 한미 반도체(042700), 원익IPS(240810), 케이씨텍(281820), 테스(095610), 파크시스템스(140860), 넥스틴(348210), SK(034730), 와이아이케이(232140), 솔브레인(357780), 한솔케미칼(014680), 유니셈(036200), 코미코(183300), 원익머티리얼즈(104830), 티씨케이(064760), 하나머티리얼즈 (166090), 원익QnC(074600), 하나마이크론(067310), 네패스(033640), 네패스아크(330860), 심텍(222800), 해성디에스(195870), 리노공업(058470), 티에스이(131290), ISC(095340), 인텍 플러스(064290), 덕산하이메탈(077360), DB하이텍(000990), 이오테크닉스(039030), 동진쎄미 켐(005290), 디엔에프(092070), 레이크머티리얼즈(281740), 메카로(241770), 코아시아 (045970), 에스앤에스텍(101490), 에이피티씨(089970)

이상 총 40개 업체를 제시했으며, 각 사 의 주목할 만한 포인트를 후반에 첨부했다.

이 중 주성엔지니어링, 한미반도체, 케이씨텍, SK, 솔브레인, 한솔케미칼, 네패스아크, 해성디에스, DB하이텍 9개 업체에 대해 커버리지를 개시하며, 최선호주는 주성엔지니어링, 한미반도체, 솔브레 인, 한솔케미칼이다.

주성엔지니어링은 DRAM Capacitor 유전막 공정 등 본업이 견조한 가운데, 소자의 구조 발전에 따른 ALD의 적용분야 확대와 더불어 공간분할 ALD 등 소자와 공정의 혁신 측면에서 공히 주도하 고 있음에 주목했다.

한미반도체는 FC-BGA 적용 확대 등에 따른 본업 성장과 더불어 NAND의 Wafer Bonding 구조 비중이 증가하고 있으며, 차세대 패키징에서 Bonding 공정의 중요도가 격상되고 있음에 주목했 다.

솔브레인과 한솔케미칼은 기존 비즈니스의 견고한 기반위에 GAA 공정향 Wet Etchant의 신규 적 용으로부터의 직접적인 수혜 영역이며, 신규 Precursor의 개발 및 출시가 활발 하는 등 반도체 수 요 성장의 중심에 있음을 주목했다.

또한, 금번 보고서를 통해 삼성전자, SK하이닉스 투자의견을 기존 각각 Trading Buy, 중립에서 매수로 상향한다.

SK하이닉스의 경우, 당사가 그간 주목해 온 메모리 업황 리스크의 상당부분이 시장에 노출되었다 고 판단한다. 특히, 최근 부각된 데이터센터의 서버 감가상각 내용연수 변경은 5년을 넘어 더 이상 장기화 되기 어려울 것으로 예상한다. 그간 리스크 부각으로 인한 주가의 횡보와 동시에 영업일수 의 경과로 Forward BPS 적용 기준을 22F에서 12개월 선행으로 변경하며, 목표주가 133,000원 으로 매수의견을 제시한다.

삼성전자의 경우, 상기 메모리 업황 리스크가 시장에 노출 되었다는 기반하에 현 시점에서는 밸류 에이션 측면에서 하방을 지지해줄 동사의 유일함(Unique)함에 주목해야 한다고 판단한다. 글로벌 유일하게 Foundry와 DRAM에 EUV를 적용해 EUV 관련 생태계를 구축하고 있으며, 최초로 Epitaxial Si 기반의 트랜지스터 채널(GAA) 양산을 앞두고 있고, 차세대 Packaging 라인업을 보유 하고 있어 Foundry+DRAM Packaging 솔루션을 유일하게 In-House로 제공할 수 있다는 점 등 이다. 실적 추정치와 목표주가(84,000원)를 유지하나, 현 주가대비 상승여력을 고려해 투자의견 매수로 상향한다.

그리고 당 산업보고서를 블로그에 정리하는 목적이 아래 표들이다.

한 눈에 보기 쉽게 잘 정리가 되어 있고, 투자 아이디어를 얻기에 최적의 자료로 생각된다.